# Improved Quality-Factor of 0.18- $\mu$ m CMOS Active Inductor by a Feedback Resistance Design

Chao-Chih Hsiao, *Associate Member, IEEE*, Chin-Wei Kuo, Chien-Chih Ho, and Yi-Jen Chan, *Senior Member, IEEE*

**Abstract**—A novel CMOS active inductor approach, which can improve the quality-factor, was presented in this report. A cascode-grounded active inductor circuit topology with a feedback resistance was proposed, which can substantially improve its equivalent inductance and quality-factor. This feedback resistance active inductor was implemented by using a 0.18- $\mu$ m 1P6M CMOS technology, which demonstrates a maximum quality-factor of 70 with a 5.7-nH inductance at 1.55 GHz, where the self-resonate frequency is 2.5 GHz. The dc power consumption of this active inductor is less than 8 mW.

**Index Terms**—Active inductor, CMOS, quality-factor.

## I. INTRODUCTION

IN THE near decade, for the increasing demands of wireless personal communication system, low cost and high integration process technologies are required to reduce the production cost and the system dimension. According to these requirements, CMOS technologies has become the best choice for wireless communication systems operating below 5 GHz. However, an important issue using standard CMOS technologies in MMIC designs is the microwave signal loss from their low-resistivity silicon substrates. With this lossy silicon substrate, the spiral inductors cannot easily achieve good performances by CMOS technologies. In the recent years, several research groups have demonstrated the integration of spiral inductors on silicon substrates with quality-factors in the range of 3~10 using multi-level spirals [1] or high-resistivity substrates [2], [3]. Another solution is using bonding wires to replace the spiral inductor, but this approach is limited to a few circuit topologies with barely any process control. An alternative method, which hasn't been studied intensively, is to implement an inductor by CMOS MMIC active devices, where the equivalent inductive impedance can be generated. The main advantages of this active inductor include the higher quality-factor, reducing chip area and potentially tunable characteristics, which can be applied on the on-chip filters, matching networks, and LC tank circuits. However, the limited operation frequency range, higher noise figure, and dc power consumption are there major drawbacks. Reports which have been attempted on this subject mainly addressed GaAs-based technologies [4] [5] in the past. A few works have carried out active inductors by CMOS technologies [6]–[9], but very few papers demonstrated the measured

results. In this report, a new CMOS high quality-factor active inductor architecture is proposed and characterized.

## II. ACTIVE INDUCTOR DESIGN

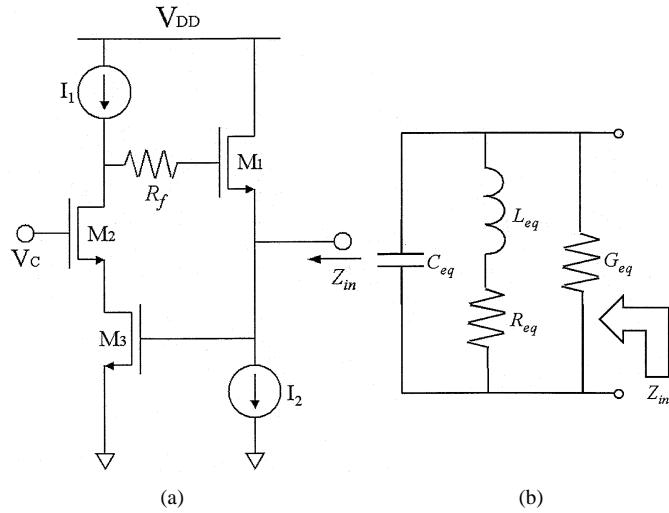

The most common active inductor topology is the grounded active inductor. This circuit topology is based on the gyrator theory, containing only two transistors, which generate an inductive impedance. This architecture of active inductors is possible to obtain several nH of inductance operating at a few GHz region. For achieving a higher inductance and a higher quality-factor, a cascode circuit topology has been proposed to reduce the output conductance ( $g_{ds}$ ) [7] by CMOS technologies. In the schematics shown in Fig. 1(a), without the resistance  $R_f$ , is the so-called cascode-grounded active inductor, by adding a transistor  $M_2$  stacks on top of the  $M_3$  to reduce the equivalent conductance. By reducing the  $g_{ds}$  in transistor  $M_3$ , the equivalent resistance decreased, and the equivalent inductance increased, as described in [7]. In order to further enhance the inductance and quality-factor of this active inductor, a feedback resistance  $R_f$  has been added between  $M_1$  and  $M_2$  in this report, as shown in Fig. 1(a). The feedback resistance  $R_f$  forms an additional inductive reactance of the impedance looking into the source terminal of  $M_1$  [10], which can significantly increase the inductance of cascode-grounded active inductor. Furthermore, the increased inductance also results in an increased quality-factor. The equivalent circuit model of the added  $R_f$  active inductor is shown in Fig. 1(b), including three parameters,  $C_{gs}$ ,  $g_{ds}$ , and  $g_m$ , to analyze this circuit, and the values of each component are expressed below.

$$C_{eq} = C_{gs3} \quad (1)$$

$$G_{eq} = \frac{2g_{ds2} + R_f g_{ds2}^2}{R_f g_{ds2} + 1} \quad (2)$$

$$R_{eq} = \frac{g_{m1}g_{ds2}g_{ds3} + \omega^2 [g_{m2}C_{gs1}^2 - g_{m1}C_{gs1}C_{gs2}(R_f g_{ds2} + 1)]}{g_{m1}^2g_{m2}g_{m3} + \omega^2 g_{m2}g_{m3}C_{gs1}^2} \quad (3)$$

$$L_{eq} = \frac{g_{m1}g_{m2}C_{gs1} + \omega^2 C_{gs1}^2 C_{gs2} (R_f g_{ds2} + 1)}{g_{m1}^2g_{m2}g_{m3} + \omega^2 g_{m2}g_{m3}C_{gs1}^2}. \quad (4)$$

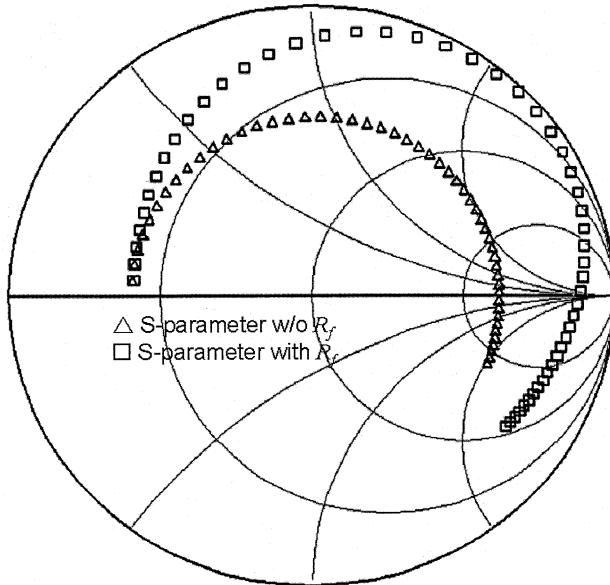

In (3) and (4), the effect of feedback resistance is  $(R_f g_{ds2} + 1)$ , which is designed to be a value larger than unity. By decreasing the equivalent resistance  $R_{eq}$ , with the help from the  $R_f$ , also results in an increase of the equivalent inductance  $L_{eq}$ . Therefore, the inductance and quality-factor can be improved in consequence. Based on these equations, the simulated one-port  $S$ -parameters are shown in Fig. 2, which illustrates that by introducing this feedback resistance in the CMOS active inductor

Manuscript received April 5, 2002; revised July 19, 2002. The review of this letter was arranged by Associate Editor Dr. Arvind Sharma.

The authors are with the Department of Electrical Engineering, National Central University, Chung li, Tao-yuan, Taiwan, R.O.C.

Digital Object Identifier 10.1109/LMWC.2002.805931

Fig. 1. (a) Schematics of cascode-grounded active inductor with a feedback resistance; (b) equivalent circuit model of this active inductor.

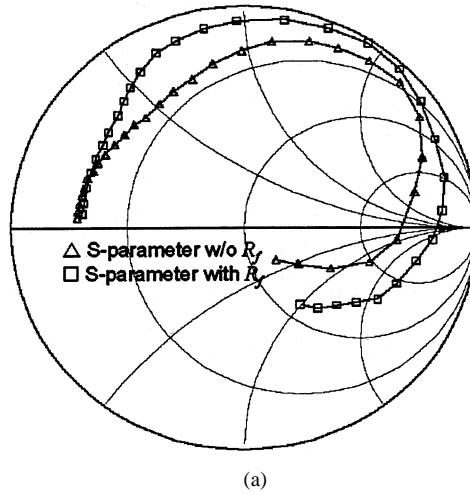

Fig. 2. Simulated  $S$ -parameters of a feedback resistance active inductor (with  $R_f$ ) and a cascode-grounded active inductor (without  $R_f$ ); the frequency region is from 100 MHz to 3.1 GHz.

design, the characteristics can be enhanced as compared with the original cascode-grounded active inductor approach, where the feedback resistance is not involved.

### III. CHARACTERISTICS OF FEEDBACK RESISTANCE ACTIVE INDUCTOR

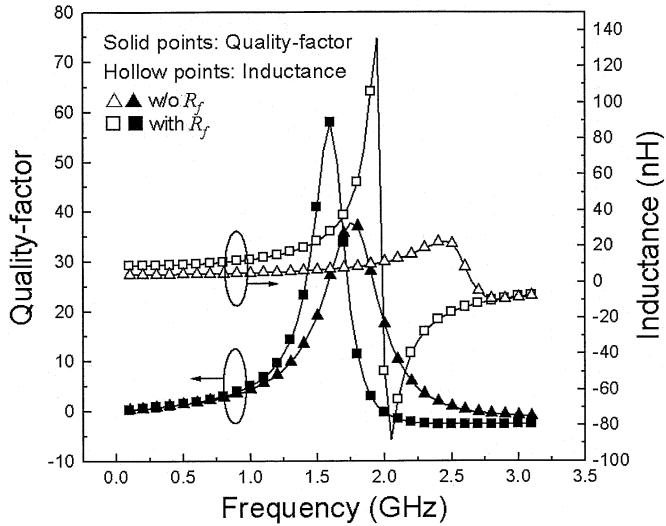

This active inductor was fabricated by a  $0.18\text{-}\mu\text{m}$  1P6M standard CMOS process, where all transistors,  $M_1$ ,  $M_2$ , and  $M_3$ , were  $50\text{-}\mu\text{m}$  channel wide n-MOSFETs to provide sufficient  $g_m$ ,  $C_{gs}$ , and  $g_{ds}$ . The performance of both the feedback resistance and cascode-grounded (without feedback resistance,  $R_f$ ) active inductors were first simulated by our homemade  $0.18\text{-}\mu\text{m}$  scalable CMOS RF large-signal model, where the additional substrate parasitics are included in this model. The simulated quality-factors and inductances are shown in Fig. 3. Max-

Fig. 3. Simulated quality-factor and inductance of a feedback resistance active inductor (with  $R_f$ ) and a cascode-grounded active inductor (without  $R_f$ ).

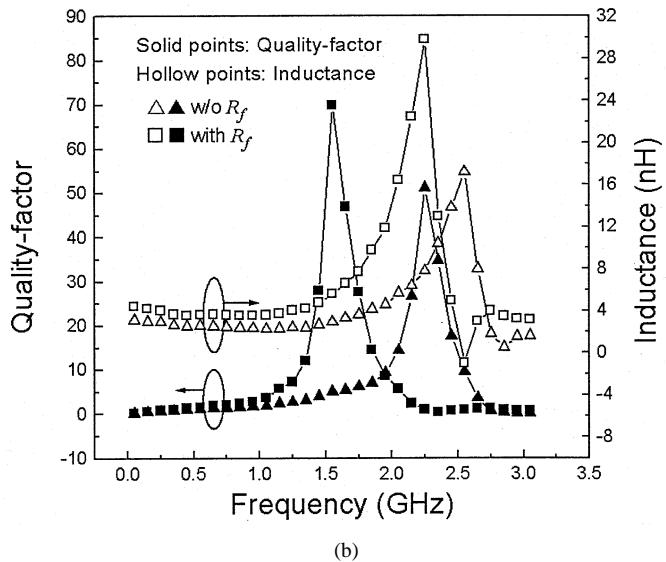

Fig. 4. (a) Measured  $S$ -parameters of a feedback resistance active inductor (with  $R_f$ ) and a cascode-grounded active inductor (without  $R_f$ ). (b) The measured quality-factor and inductance of feedback resistance active inductor and cascode-grounded active inductor.

imum simulated quality-factors of feedback resistance and cascode-grounded (without  $R_f$ ) active inductors are 60 and 36, corresponding to an inductance of 10 nH and 5 nH, respectively. Because of the increased inductance, the self-resonate frequency of feedback resistance active inductor becomes lower, i.e., 2.0 GHz versus 2.7 GHz.

The measured  $S$ -parameters, which demonstrate the same trend as the simulated results, were carried out by a network analyzer. According to the measured results, the equivalent inductance and quality-factor can be easily obtained from the one port  $S$ -parameters. Fig. 4(a) shows the one-port  $S$ -parameters of both with and without feedback resistance active inductors, and these measured characteristics are similar to the predictions of derived equations, shown in Fig. 2, where the improved performance can be obtained by adding the feedback resistance. Fig. 4(b) illustrates the measured quality-factor and inductance of feedback resistance and cascode-grounded (without  $R_f$ ) active inductors. The supplied voltage  $V_{DD}$  of this active inductor is 2 V with a 4-mA dc current, and the total power consumption is 8 mW. The maximum quality-factor of feedback resistance active inductor is 70 at 1.55 GHz with a 5.7-nH inductance and the self-resonate frequency is 2.5 GHz. As for the CMOS active inductor, without the feedback resistance, these values are 51 at 2.2 GHz and the self-resonate frequency is 2.8 GHz. Due to the additional parasitic effects, the measured inductances are smaller than simulation ones. To compare with spiral inductors from the same standard CMOS process, spiral inductors with multilayer interconnects were also fabricated. Spiral inductors demonstrate the same inductance between 5 and 7 nH, where the quality-factor is between 6 and 7.5. The active inductor achieves much higher quality-factor but a lower self-resonate frequency. In the meantime, this active inductor requires only  $88 \times 90 \mu\text{m}^2$  chip area, which is much smaller than the on-chip spiral inductors.

#### IV. CONCLUSIONS

This report demonstrates a high quality-factor CMOS active inductor with a novel configuration by a 0.18- $\mu$ m CMOS tech-

nology. By introducing a feedback resistor  $R_f$  to a cascode-grounded active inductor, the inductance and quality-factor can be enhanced by this approach. The maximum quality-factor is 70 corresponding to an inductance of 5.7 nH, where this active inductor also consumes 8-mW dc power.

#### ACKNOWLEDGMENT

The authors are grateful to the UMC and Novatek, for providing the CMOS foundry service.

#### REFERENCES

- [1] J. N. Burghartz, K. A. Jenkins, and M. Soyuer, "Multilevel-spiral inductors using VLSI interconnect technology," *IEEE Electron Device Lett.*, vol. 17, pp. 428–430, Sept. 1996.

- [2] M. Park, S. Lee, H. K. Yu, J. G. Koo, and K. S. Nam, "High Q CMOS-compatible microwave inductors using double-metal interconnection silicon technology," *IEEE Microwave Guided Wave Lett.*, vol. 7, pp. 45–47, Feb. 1997.

- [3] P. Q. Chen and Y. J. Chan, "Improved microwave performance on low-resistivity Si substrates by Si<sup>+</sup> ion implantation," *IEEE Trans. Microwave Theory Tech.*, vol. 48, pp. 1582–1585, Sept. 2000.

- [4] S. Hara, T. Tokumitsu, T. Tanaka, and M. Aikawa, "Broad band monolithic microwave active inductor and its application to miniaturise wide band amplifiers," *IEEE Trans. Microwave Theory Tech.*, vol. 36, pp. 1920–1924, Dec. 1988.

- [5] S. G. El Khoury, "New approach to the design of active floating inductors in MMIC technology," *IEEE Trans. Microwave Theory Tech.*, vol. 44, pp. 505–512, Apr. 1996.

- [6] A. Pascht, J. Fischer, and M. Beertho, "A CMOS low noise amplifier at 2.4 GHz with active inductor load," in *Silicon Monolithic Integrated Circuits RF Syst., Tech. Dig.*, 2001, pp. 1–5.

- [7] A. Thanachayanont and A. Payne, "VHF CMOS integrated active inductor," *Electron. Lett.*, vol. 32, pp. 999–1000, May 1996.

- [8] G. Mascarenhas, J. Caldinhas Vaz, and J. Costa Freire, "CMOS active inductors for L band," in *Asia-Pacific Microwave Conf., Tech. Dig.*, 2000, pp. 157–160.

- [9] J. N. Yang, Y. C. Cheng, T. Y. Hsu, T. R. Hsu, and C. Y. Lee, "A 1.75 GHz inductor-less CMOS low noise amplifier with high-Q active inductor load," in *Midwest Symp. Circuits Syst., Tech. Dig.*, vol. 2, 2001, pp. 816–819.

- [10] I. E. Ho and R. L. Van Tuyl, "Inductorless monolithic microwave amplifiers with directly cascaded cells," in *IEEE MTT-S Tech. Dig.*, vol. 1, May 1990, pp. 515–518.